10.10 Flip Flop Application

1. TUJUAN[kembali]

a. mengetahui pengaplikasian dari Flip-Flop

b. mengetahui spesifikasi dari alat-alat yang digunakan dengan datasheet yang didapat

2. ALAT DAN BAHAN[kembali]

ALAT :

1. Power Supply

BAHAN :

1. Resistor

-. Switch mekanik

Gambar 9 Switch Mekanik

Switch adalah salah satu komponen yang penting dalam setiap rangkaian atau perangkat elektronik. Seperti pada artikel yang disebutkan sebelumnya, Saklar atau Switch adalah perangkat yang digunakan untuk memutuskan atau menghubungkan aliran arus listrik. Meskipun saat ini telah banyak yang menggunakan saklar atau switch elektronik yang menggunakan sensor ataupun rangkaian yang terdiri komponen semikonduktor seperti transistor, IC dan dioda. Namun saklar mekanik atau mechanical switch masih tetap memegang peranan penting pada hampir semua perangkat atau peralatan listrik dan elektronik.

3. Dasar Teori[kembali]

Flip-flop digunakan dalam berbagai rangkaian aplikasi, yang paling umum di antaranya adalah rangkaian pembagian frekuensi dan penghitungan serta rangkaian penyimpanan dan transfer data. Area aplikasi ini dibahas panjang lebar di Bab 11 tentang penghitung dan register. Kedua aplikasi ini menggunakan susunan sandal jepit bertingkat dengan atau tanpa beberapa logika kombinasional tambahan untuk menjalankan fungsi yang diinginkan. Penghitung dan register tersedia dalam bentuk IC untuk berbagai aplikasi rangkaian digital. Aplikasi lain dari sandal jepit termasuk penggunaannya untuk sakelar debouncing, di mana bahkan flip-flop yang tidak di-clock (seperti kait NAND atau NOR) dapat digunakan, untuk menyinkronkan input asinkron dengan input jam dan untuk identifikasi tepi input sinkron . Ini secara singkat dijelaskan dalam paragraf berikut.

10.10.1 Switch Debouncing

Karena fenomena pantulan sakelar, sakelar mekanis tidak dapat digunakan sedemikian rupa untuk menghasilkan transisi tegangan yang bersih. Lihat Gambar 10.47 (a). Ketika sakelar dipindahkan dari posisi 1 ke posisi 2, yang diinginkan pada output adalah transisi tegangan bersih dari 0 ke + V volt, seperti yang ditunjukkan pada Gambar 10.47 (b). Apa yang sebenarnya terjadi ditunjukkan pada Gambar 10.47 ( c). Output membuat beberapa transisi antara 0 dan + V volt selama beberapa milidetik karena kontak pantulan sebelum akhirnya menetap di + V. volt. Demikian pula, ketika dipindahkan dari posisi 2 kembali ke posisi 1, ia membuat beberapa transisi sebelum berhenti pada 0 V. Meskipun perilaku acak ini hanya berlangsung selama beberapa milidetik, perilaku acak ini tidak dapat diterima untuk banyak aplikasi rangkaian digital. NAND atau kait NOR dapat mengatasi masalah ini dan memberikan transisi keluaran yang bersih. Gambar 10.48 menunjukkan rangkaian pantulan sakelar tipikal yang dibangun di sekitar kait NAND. Rangkaian berfungsi sebagai berikut.

Saat sakelar berada di posisi 1, output berada pada level '0'. Ketika dipindahkan ke posisi 2, output pergi ke level '1' dalam beberapa nanodetik (tergantung pada penundaan propagasi gerbang NAND) setelah kontak pertama dengan posisi 2. Saat kontak sakelar memantul, itu membuat dan putus kontak dengan posisi 2 sebelum akhirnya menetap di posisi yang diinginkan. Pembuatan kontak selalu mengarah ke level '1' pada output, dan putusnya kontak juga mengarah ke level '1' pada output karena fakta bahwa pemutusan kontak menghasilkan level '1' pada kedua input kait yang memaksa keluaran untuk menahan keadaan logika yang ada. Fakta bahwa ketika sakelar dibawa kembali ke posisi 1, output membuat transisi yang rapi ke level '0' dapat dijelaskan pada baris yang sama.

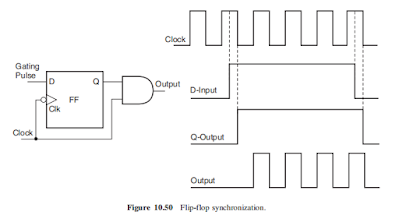

10.10.2 Flip-Flop Synchronization

Pertimbangkan situasi di mana input jam tertentu, yang bekerja dalam hubungannya dengan berbagai input sinkron, akan di-gated dengan pulsa gating yang dibangkitkan secara tidak sinkron, seperti yang ditunjukkan pada Gambar 10.49. Output dalam hal ini memiliki pulsa clock di salah satu atau kedua ujungnya diperpendek lebarnya, seperti yang ditunjukkan pada Gambar 10.49. Masalah ini dapat diatasi dan operasi gating disinkronkan dengan bantuan flip-flop, seperti yang ditunjukkan pada Gambar 10.50.

10.10.3 Detecting the Sequence of Edges

Flip-flops juga dapat digunakan untuk mendeteksi urutan kemunculan tepi naik dan turun. Gambar 10.51 menunjukkan bagaimana flip-flop dapat digunakan untuk mendeteksi apakah tepi positif A mengikuti atau mendahului tepi positif lainnya B. Kedua tepi tersebut masing-masing diterapkan ke input D dan clock input dari flip- D yang dipicu tepi positif flip-flop. Jika tepi A tiba lebih dulu, kemudian, saat tepi B tiba, keluarannya berubah dari 0 ke 1. Jika sebaliknya, ia tetap pada tingkat '0'.

4. Percobaan[kembali]

a. Prosedur Percobaan

1) Buka aplikasi proteus

2) Pilih komponen yang dibutuhkan, pada rangkaian ini.

3) Rangkai setiap komponen menjadi rangkaian yang diinginkan

4) Ubah spesifikasi komponen sesuai kebutuhan

5) Jalankan simulasi rangkaian.

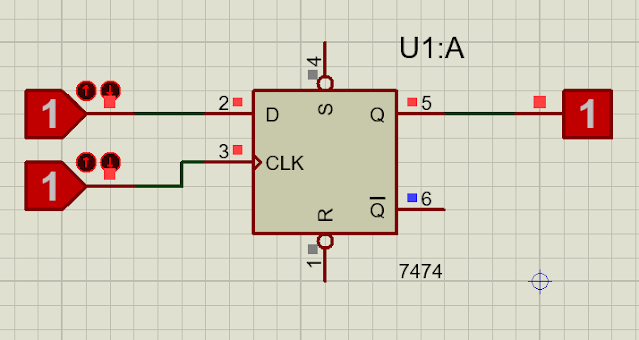

b. Rangkaian Simulasi

5. Problem[kembali]

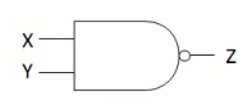

1. Buatlah tabel kebenaran gerbang di bawah ini!

Jawab :

2. Buatlah berbagai simbol dari complementary gate!

Jawab :

6. Contoh Soal[kembali]

Gambar 10.52 menunjukkan dua bentuk gelombang berpulsa A dan B, dengan bentuk gelombang A memimpin bentuk gelombang B dalam fase, seperti yang ditunjukkan pada gambar. Sarankan rangkaian flip-flop untuk mendeteksi kondisi ini dengan menghasilkan (a) keluaran Q logika '1' dan (b) keluaran Q logika '0'.

Jawab :

(a) Flip-flop D yang dipicu tepi positif, seperti yang ditunjukkan pada Gambar 10.53 (a), dapat digunakan untuk tujuan tersebut. Bentuk gelombang A diterapkan ke masukan D, dan bentuk gelombang B diterapkan ke masukan clock. Jika kita memeriksa dua bentuk gelombang, kita akan menemukan bahwa, pada setiap kemunculan tepi depan bentuk gelombang B, bentuk gelombang A berada dalam keadaan logika '1'. Jadi, keluaran Q dalam hal ini akan selalu dalam keadaan logika '1'.

(b) Dengan menukar koneksi bentuk gelombang A dan B seperti yang ditunjukkan pada Gambar 10.53 (b), keluaran Q akan berada dalam keadaan logika '0' selama bentuk gelombang A mengarah pada bentuk gelombang B dalam fase. Dalam hal ini, pada setiap kemunculan tepi depan bentuk gelombang A (masukan clock), bentuk gelombang B (masukan D) berada dalam keadaan logika '0'.

Tidak ada komentar:

Posting Komentar